The goal of this project is to add a PLL lock detection feature to the original GPSDO design by G3RUH (http://www.jrmiller.demon.co.uk/projects/ministd/frqstd.htm).

I have modified the PCB by adding a lock detection circuit based on the monitoring of the PWM signal used to drive the OCXO VTUNE. A spare XOR gate of the 74HCT86 is used to output this signal on the DB9 pin 9 without disturbing the analog loop.

The lock detection job is done by a PICAXE-18X MCU and a 1K/10µF RC filter connected to the analog input (0-5V range). The lock condition is detected by measuring the stability of this signal over 1 minute. Alternatively, one can measure directly the PWM duty cycle with the counting feature of an MCU. That is not the solution I have chosen because the PICAXE pulse width measurement feature does not provide enough resolution.

Additionally, the GPS NMEA output is monitored for satellite and GPS signal quality reporting.

Everything has been integrated in a nice aluminium enclosure with DIY face plate.

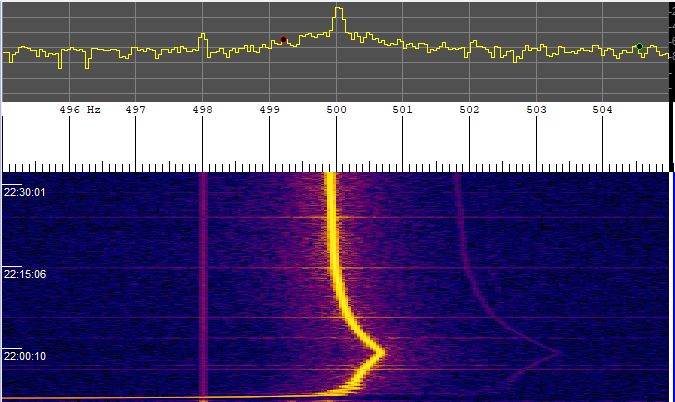

Here is the spectrogram of the 10 MHz output monitored with an ANAN-100D TRX and SpectrumLab. The GPSDO needs about 30 min for stabilization.